# HMC436MS8G

# GaAs MMIC DPDT DIVERSITY SWITCH, 4.9 - 5.9 GHz

### **Typical Applications**

This switch is ideal for use as a DPDT Diversity Switch for 4.9 - 5.9 GHz applications:

- HiperLAN & 802.11a WLAN

- UNII Radios

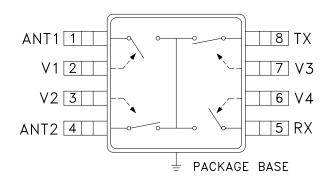

### Functional Diagram

#### **Features**

Low Insertion Loss: 1.0 dB

High IP3: +50 dBm

P1dB Compression: 1 Watt Positive Control: 0/+3V

Ultra Small MSOP8G Package: 14.8 mm<sup>2</sup>

### **General Description**

The HMC436MS8G is a low cost C-band DPDT switch that operates between 4.9 and 5.9 GHz. This switch can operate as an integrated antenna diversity and transmit/receive switch for the 802.11a/HiperLAN and UNII radio platforms. The design provides 20 dB of isolation between antennas and between Tx and Rx ports. The switch features 1 dB insertion loss and high power handling capability. Switch state is controlled using four control voltage lines toggled between 0 and +3 to +5V.

# Electrical Specifications,

$T_A = +25^{\circ}$  C, Vctl = 0/+3 Vdc (Unless Otherwise Stated), 50 Ohm System

| Parameter                                                                |                                                                | Frequency                                       | Min.           | Тур.           | Max.       | Units      |

|--------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|----------------|----------------|------------|------------|

| Insertion Loss                                                           |                                                                | 4.9 - 5.1 GHz<br>5.1 - 5.9 GHz                  |                | 1.2<br>1.0     | 1.5<br>1.3 | dB         |

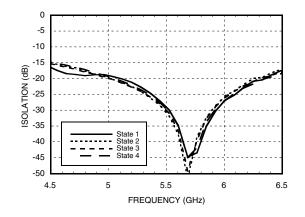

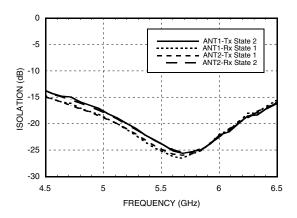

| Isolation                                                                |                                                                | 4.9 - 5.1 GHz<br>5.1 - 5.4 GHz<br>5.4 - 5.9 GHz | 14<br>16<br>20 | 18<br>20<br>25 |            | dB<br>dB   |

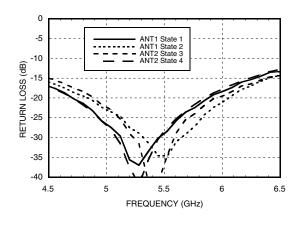

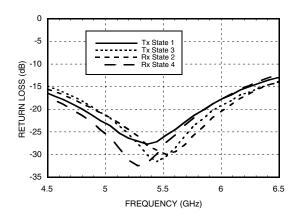

| Return Loss (On State, Any Port)                                         |                                                                | 4.9 - 5.1 GHz<br>5.1 - 5.4 GHz<br>5.4 - 5.9 GHz | 17<br>16<br>13 | 20<br>20<br>17 |            | dB<br>dB   |

| Input Power for 1 dB Compression                                         | Vctl= 0/+3V<br>Vctl= 0/+5V                                     | 4.9 - 5.9 GHz                                   | 27<br>30       | 30<br>33       |            | dBm<br>dBm |

| Input Power for 0.1 dB Compression                                       | Vctl= 0/+3V<br>Vctl= 0/+5V                                     | 4.9 - 5.9 GHz                                   | 23<br>29       | 26<br>32       |            | dBm<br>dBm |

| Input Third Order Intercept<br>(Two-Tone Input Power= +17 dBm Each Tone) | Vctl= 0/+3V<br>Vctl= 0/+5V                                     | 4.9 - 5.9 GHz                                   | 47<br>49       | 50<br>52       |            | dBm<br>dBm |

| Switching Characteristics                                                | tRISE / tFALL (10/90% RF)<br>tON / tOFF (50% CTL to 10/90% RF) | 4.9 - 5.9 GHz                                   |                | 10<br>25       |            | ns<br>ns   |

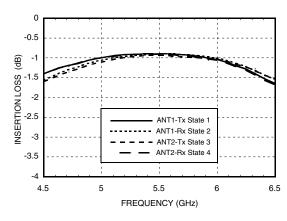

#### Insertion Loss

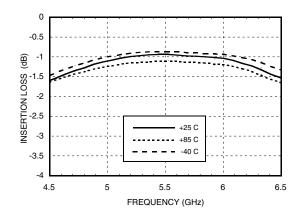

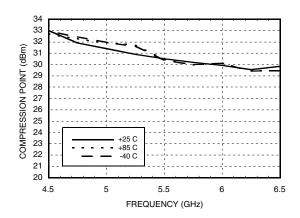

#### Insertion Loss vs. Temperature

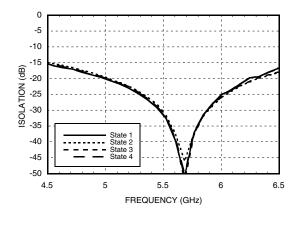

#### Isolation, Tx & Rx

Isolation, ANT1 & ANT2

#### Return Loss, ANT1 & ANT2

Return Loss, Tx & Rx

#### Isolation, ANT1 / ANT2 - Tx / Rx

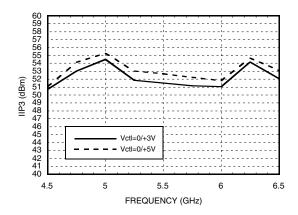

Input IP3 \*

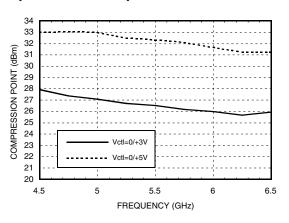

Input 0.1 dB Compression Point

Input 1 dB Compression Point, Vctl= 0/+3V

### **Control Voltages**

| State | Bias Condition                |

|-------|-------------------------------|

| Low   | 0 to +0.5 Vdc @ 20 μA         |

| High  | +3.0 to +5.5 Vdc @ 20 μA Typ. |

#### Truth Table

| Path      | V1   | V2   | V3   | V4   | State |

|-----------|------|------|------|------|-------|

| ANT1 - Tx | High | Low  | High | Low  | 1     |

| ANT1 - Rx | High | Low  | Low  | High | 2     |

| ANT2 - Tx | Low  | High | High | Low  | 3     |

| ANT2 - Rx | Low  | High | Low  | High | 4     |

| All Off*  | Low  | Low  | Low  | Low  | 5     |

<sup>\*</sup> External components are necessary if "all off" isolation state is desired. See HMC436MS8G product note.

<sup>\*</sup> Two-tone input power = +17 dBm each tone, 1 MHz spacing.

### Absolute Maximum Ratings

| RF Input Power Vctl= 0/+3V             | +30 dBm          |  |

|----------------------------------------|------------------|--|

| Control Voltage Range (V1, V2, V3, V4) | -0.5 to +7.5 Vdc |  |

| Storage Temperature                    | -65 to +150 °C   |  |

| Operating Temperature                  | -40 to +85 °C    |  |

Caution: Do not "Hot Switch" power levels greater than +23 dBm (Vctl = 0/+3 Vdc).

DC blocking capacitors are required at ports ANT1, ANT2, Tx, Rx.

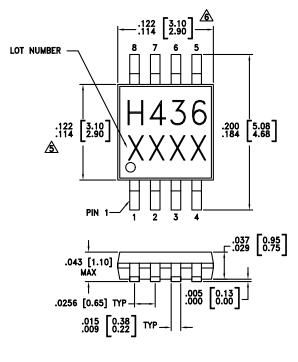

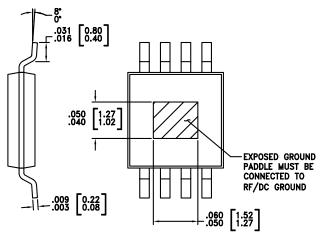

### **Outline Drawing**

#### NOTES:

- PACKAGE BODY MATERIAL: LOW STRESS INJECTION MOLDED PLASTIC SILICA AND SILICON IMPREGNATED.

- 2. LEADFRAME MATERIAL: COPPER ALLOY

- 3. LEADFRAME PLATING: Sn/Pb SOLDER

- 4. DIMENSIONS ARE IN INCHES [MILLIMETERS].

- /5\ DIMENSION DOES NOT INCLUDE MOLDFLASH OF 0.15mm PER SIDE.

- 6 DIMENSION DOES NOT INCLUDE MOLDFLASH OF 0.25mm PER SIDE.

- 7. ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GROUND.

## Pin Descriptions

| Pin Number | Function       | Description                                                                            | Interface Schematic |

|------------|----------------|----------------------------------------------------------------------------------------|---------------------|

| 1, 4       | ANT1, ANT2     | These pins are DC coupled and matched to 50 Ohms.<br>Blocking capacitors are required. |                     |

| 2, 3, 6, 7 | V1, V2, V4, V3 | See truth and control voltage tables.                                                  | R c                 |

| 5, 8       | Rx, Tx         | These pins are DC coupled and matched to 50 Ohms.<br>Blocking capacitors are required. |                     |

|            | GND            | Package bottom has exposed metal paddle that must be connected to PCB RF ground.       | <u> </u>            |

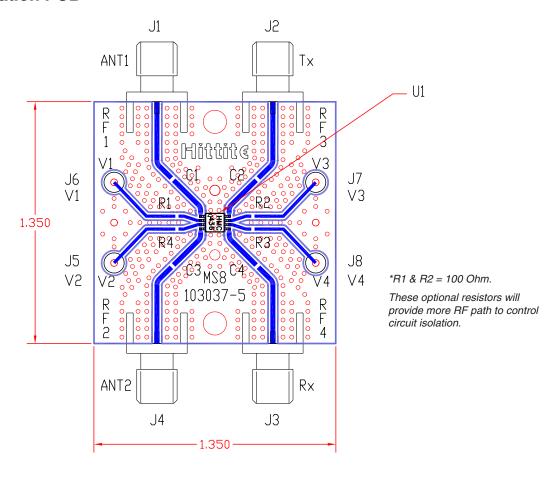

#### **Evaluation PCB**

#### List of Material

| Item                                  | Description                       |

|---------------------------------------|-----------------------------------|

| J1 - J4                               | PC Mount SMA Connector            |

| J5 - J8                               | DC Pin                            |

| C1 - C4                               | 100 pF Capacitor, 0402 Pkg.       |

| R1 - R2                               | 100 Ohm Resistor, 0402 Pkg.       |

| U1                                    | HMC436MS8G DPDT Diversity Switch  |

| PCB*                                  | 103037 Evaluation PCB 1.5" x 1.5" |

| * Circuit Board Material: Rogers 4350 |                                   |

The circuit board used in the final application should use RF circuit design techniques. Signal lines should have 50 ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown above. A sufficient number of VIA holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown above is available from Hittite upon request.